该多功能时钟系统包括:

可以控制模式,计时器或者时钟,通过按键控制,数码管实时显示时分秒,led显示计时状态。

时-分-秒显示,为24小时制

通过按键可以动态调整时间

通过按键可以动态选择要调整的时间,对应的数码管闪烁

按键消抖、看门狗电路等

系统包括下列模块:

分频模块,计数模块,按键模块,看门狗模块,数码管模块,计时器模块,选择模块等。

使用VHDL语言实现

在quartus下实现,也可在vivado下:

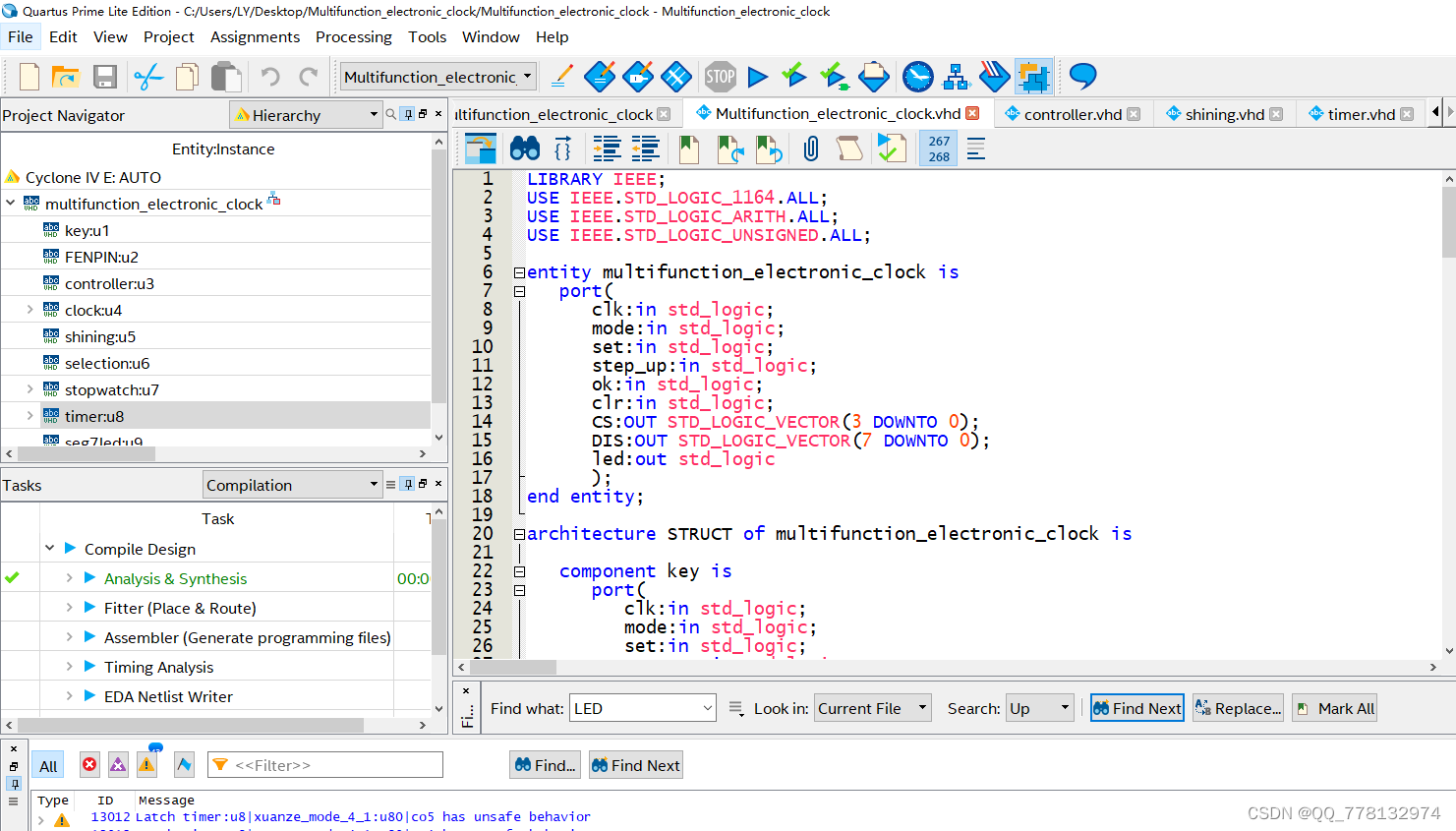

下面为quartus工程截图:

下面为顶层模块代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multifunction_electronic_clock is

port(

clk:in std_logic;

mode:in std_logic;

set:in std_logic;

step_up:in std_logic;

ok:in std_logic;

clr:in std_logic;

CS:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

DIS:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

led:out std_logic

);