一、GPIO外设的概述

基础概念

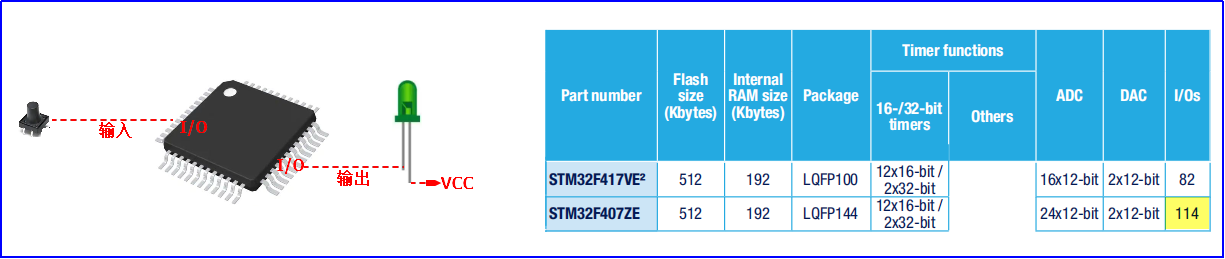

GPIO(General Purpose Input/Output,通用输入/输出接口,通常简称为I/O口)外设是现代微控制器MCU中最基础、应用最广泛的核心接口模块,主要用于实现芯片与外部电子设备之间的双向交互。

作为MCU的标准配置,GPIO引脚本质上是一种可编程的数字信号接口,其核心功能是作为通用的数字输入或输出通道。通过灵活的软件配置,工程师可以根据具体应用场景将GPIO设置为多种工作模式,包括但不限于推挽输出、开漏输出、上拉/下拉输入、浮空输入等模式,从而满足不同外设的接口需求。

在实际应用中,GPIO引脚需要与各类外部设备(如传感器、执行器、显示器等)建立物理连接,通过这种连接方式,MCU既可以向外设发送控制指令,也能够实时采集外设的状态数据,实现双向的数据交换和通信功能。这种简单而强大的接口特性,使得GPIO成为嵌入式系统开发中最常用、最基础的外设接口之一。

电平概念

在嵌入式系统开发中,I/O口操作是一项基础且重要的功能,它主要涉及对芯片某个输入/输出端口进行电平控制与状态检测。具体而言,这种操作包含两个核心功能:一方面是通过编程控制I/O口的输出电平,可以将其设置为高电平或低电平状态,另一方面则是利用I/O口的输入功能,实时读取外部电路输入的电平状态。

电平是衡量电信号强弱或状态的物理量,通常以电压或电流的相对大小表示,是电子电路中传递信息的基础。在电子技术中,电平本质是电路中某点与参考点(通常为地)之间的电压差(电压电平)或电流值(电流电平),用于描述信号的幅度范围、逻辑状态或能量强弱,所以电平并不是一个非常准确的值,而是可以用一个范围表示。

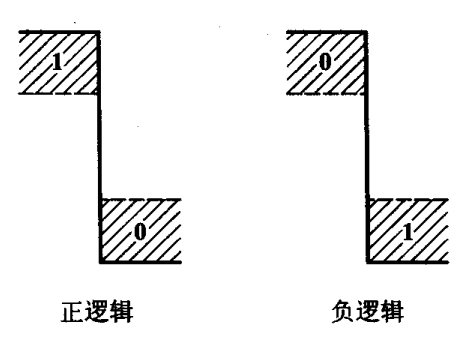

电平是相对概念,需要通过与基准值(例如电源电压、地电位)对比来定义高/低或具体数值,在数字电路中,电平主要用于表示逻辑状态(0/1),其中又可以把电平分为正逻辑电平和负逻辑电平。

电平规范

常用的电平规范包含TTL和CMOS电平,其中TTL电平基于双极型晶体管的电流驱动逻辑,以5V固定电压供电,功耗较高且抗干扰能力较弱,曾是早期数字电路主流,如今已逐步被替代,而CMOS电平采用MOS管互补结构的电压驱动设计,支持3.3V、1.8V等灵活电压,功耗极低且抗干扰能力强,凭借低功耗与高兼容性成为现代电路核心。

| 逻辑电平 |

Vcc/V |

VOH/V |

VOL/V |

VIH/V |

VIL/V |

| TTL |

5.0 |

≥2.4 |

≤0.4 |

≥2.0 |

≤0.8 |

| LVTTL |

3.3 |

≥2.4 |

≤0.4 |

≥2.0 |

≤0.8 |

| CMOS |

5.0 |

≥4.45 |

≤0.5 |

≥3.5 |

≤1.5 |

| LVCMOS |

3.3 |

≥3.2 |

≤0.1 |

≥2.0 |

≤0.7 |

在当前嵌入式开发中,CMOS电平的低电压版本是绝对主流,广泛应用于微控制器(例如STM32)、传感器、通信接口(如UART、SPI、I2C)等场景,其灵活的电压适配与低功耗特性完美契合嵌入式设备对能效和小型化的需求,而传统TTL电平仅在部分老旧工业设备中偶尔使用,目前已经不是开发首选电平规范。

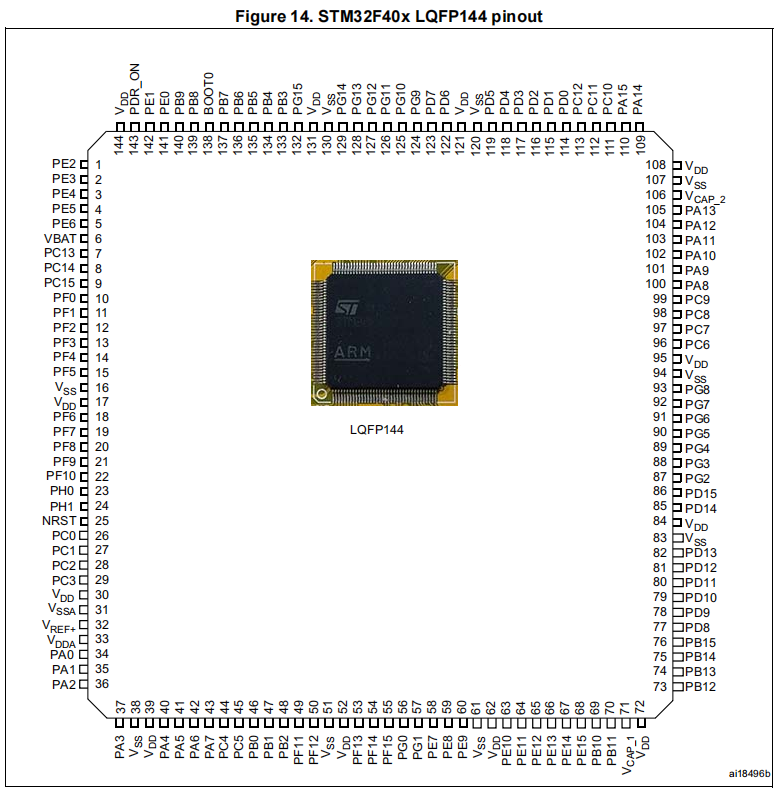

管脚布局

-

电源引脚

VCC、VDD、VSS、VDDA、VSSA、VREF+等都属于电源相关的引脚类别,它们在电路中主要负责为芯片和外围元器件提供稳定的工作电压,确保各个功能模块能够正常运作。其中VCC和VDD通常表示正电源输入端,VSS表示接地端,VDDA和VSSA是模拟电源引脚,VREF+则用于提供参考电压。

-

晶振引脚

PC14、PC15、PH0、PH1这几组引脚被设计为晶振接口引脚,主要用于连接外部晶振电路,为芯片提供精确的时钟信号。这些引脚具有复用功能,在不需要使用晶振的场合下,也可以重新配置为普通的GPIO或其他特殊功能引脚,增加了设计的灵活性。

-

复位引脚

NRST是专门用于系统复位的引脚,它采用低电平有效的复位方式,当该引脚接收到持续的低电平信号时,芯片会执行复位操作,使整个系统恢复到初始状态。这种设计有助于在系统出现异常时快速恢复。

-

BOOT引脚

BOOT0是一个专用的启动模式选择引脚,而BOOT1则可作为普通功能引脚使用。这两个引脚共同作用,通过不同的电平组合可以设置芯片的自举模式,决定芯片上电后从哪个存储区域启动程序,这在系统调试和程序升级时非常有用。

-

GPIO引脚

该芯片采用144引脚的封装形式,其中通用输入输出(GPIO)引脚就占用了114个。这些GPIO引脚具有高度的可配置性,可以通过软件设置为输入或输出模式,还能配置不同的工作参数,为外部设备提供灵活的接口方案。

-

下载引脚

PA13、PA14、PB3、PB4等引脚被分配为程序下载接口,支持JTAG和SWD两种主流的调试下载协议。这些引脚在系统开发阶段尤为重要,既可以用于程序烧录,也可用于在线调试,大大提高了开发效率。

引脚命名

在集成电路设计领域,芯片制造商在进行芯片架构规划时,会按照行业通用标准对芯片的管脚进行系统性的命名规范。这种命名体系通常遵循国际通用的惯例,具有高度的统一性和标准化特征。具体而言,输入输出端口(IO口)的命名一般以英文字母"P"(代表Pin,即引脚)作为前缀标识。为了便于管理和使用,这些IO口会被划分为若干个功能组(或称端口组),每个端口组采用从A到H的大写字母进行顺序命名标记。

根据行业标准实践,每个端口组内部会包含16个独立的物理引脚,这些引脚的编号采用数字编码方式,从0开始依次递增至15。

基于这套命名规则,大家可以清晰地表示各个端口组的引脚分布:例如A端口组的引脚完整命名范围为从PA0开始直到PA15,B端口组的引脚则被命名为PB0至PB15,以此类推,其他端口组(C、D、E、F、G、H等)也遵循相同的命名逻辑,确保整个芯片的引脚命名系统既规范又有条理,便于工程师在电路设计和调试过程中快速准确地定位和使用各个功能引脚。

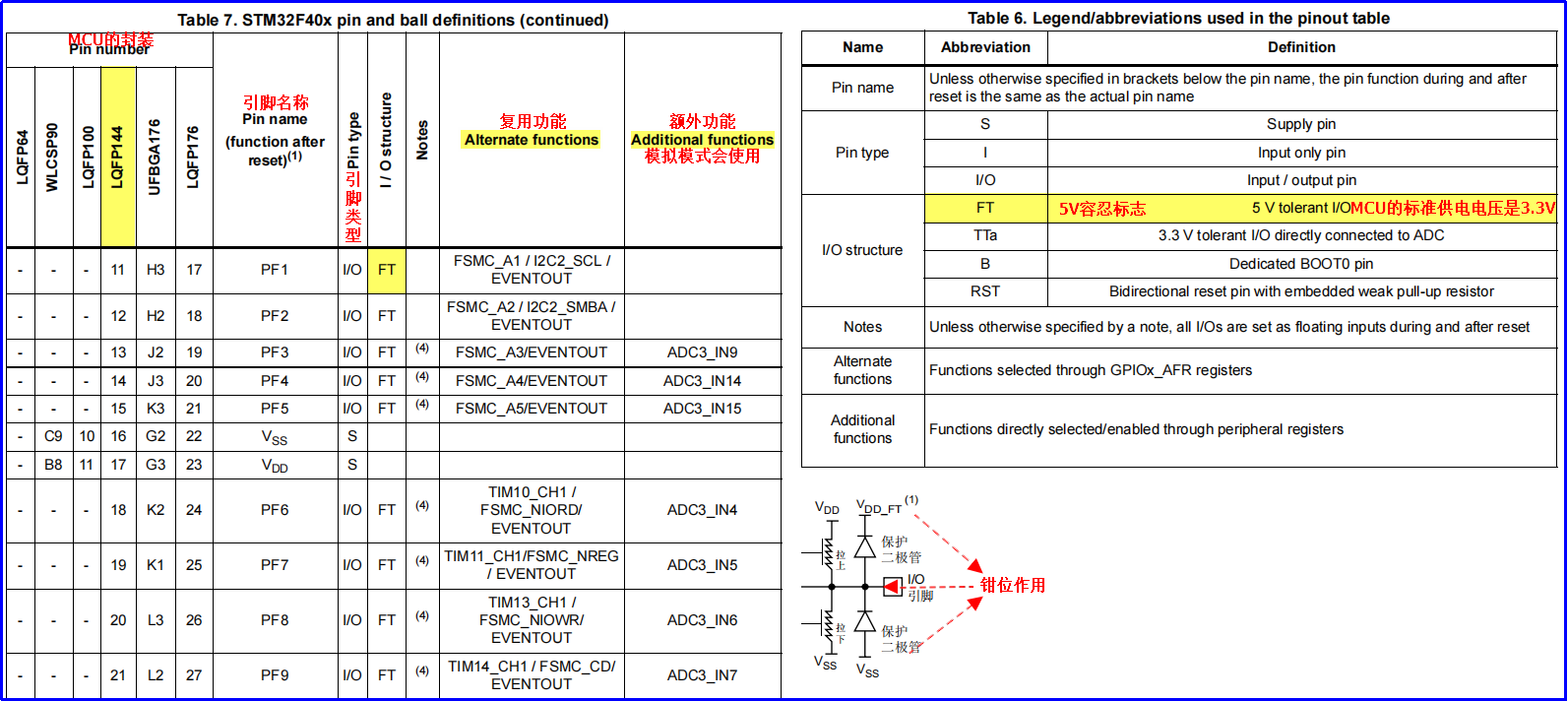

引脚功能

在实际应用过程中,需要特别注意的是,微控制器芯片的每个引脚都具有多种不同的功能配置。通常情况下,默认状态下引脚都被设置为通用输入输出(GPIO)模式,这是最基本也是最常用的功能模式。

然而,除了基本的GPIO功能外,这些引脚往往还具有所谓的"第二功能"或"复用功能",这些功能包括但不限于UART通信、PWM输出、I2C接口等特殊功能。

特别需要强调的是,当需要使用模数转换(ADC)通道或数模转换(DAC)功能时,必须将相应引脚配置为模拟模式。而其他情况下,若要将引脚作为非GPIO功能使用,则必须将引脚设置为复用模式。

由于不同芯片厂商、不同型号的芯片其引脚功能定义可能差异很大,因此在实际项目开发中,若要准确了解具体引脚的各项功能定义、工作模式及配置方法,必须仔细查阅该芯片的官方数据手册(Datasheet)或参考手册(Reference Manual)!!!!

二、GPIO外设的原理与应用

背景说明

想要学习硬件开发,通常都是从最简单的LED灯控制开始入手。这主要是因为LED作为最基本的外设元件,具有电路结构简单、操作直观的特点,非常适合作为硬件开发的入门实验。

通过点亮LED这个基础项目,大家可以逐步掌握硬件开发的基本流程,包括电路连接、程序编写、调试测试等环节,进而理解外设控制的核心原理和方法。LED控制虽然看似简单,但却涵盖了硬件开发中最基础也是最重要的知识要点,为后续学习更复杂的外设控制打下了坚实的基础。

开发流程

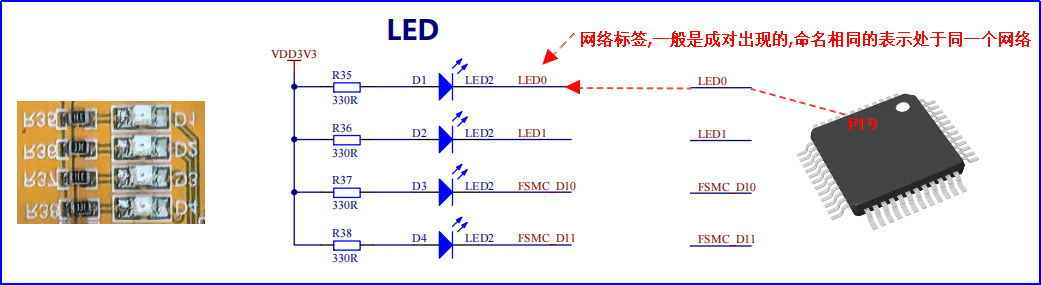

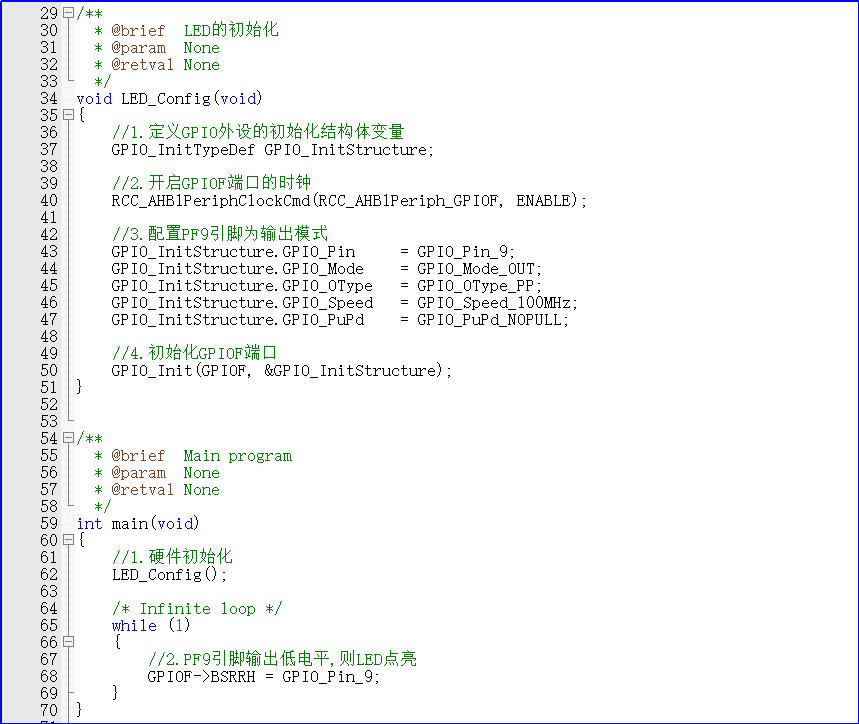

1、查看原理图,找到控制发光二极管的芯片的IO口,LED0 -- PF9引脚,其他的引脚类似!!

- 分析原理图,理解硬件的控制原理(复杂外设还需要结合数据手册),输出低电平就亮

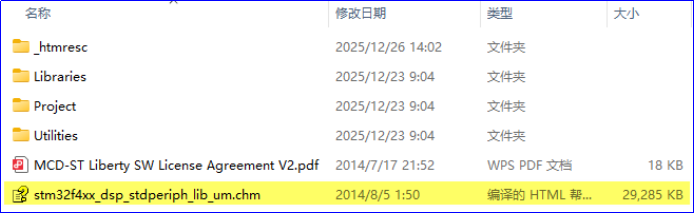

- 程序设计,根据ST公司提供的函数库(标准外设库/HAL库)的帮助手册学习开发流程

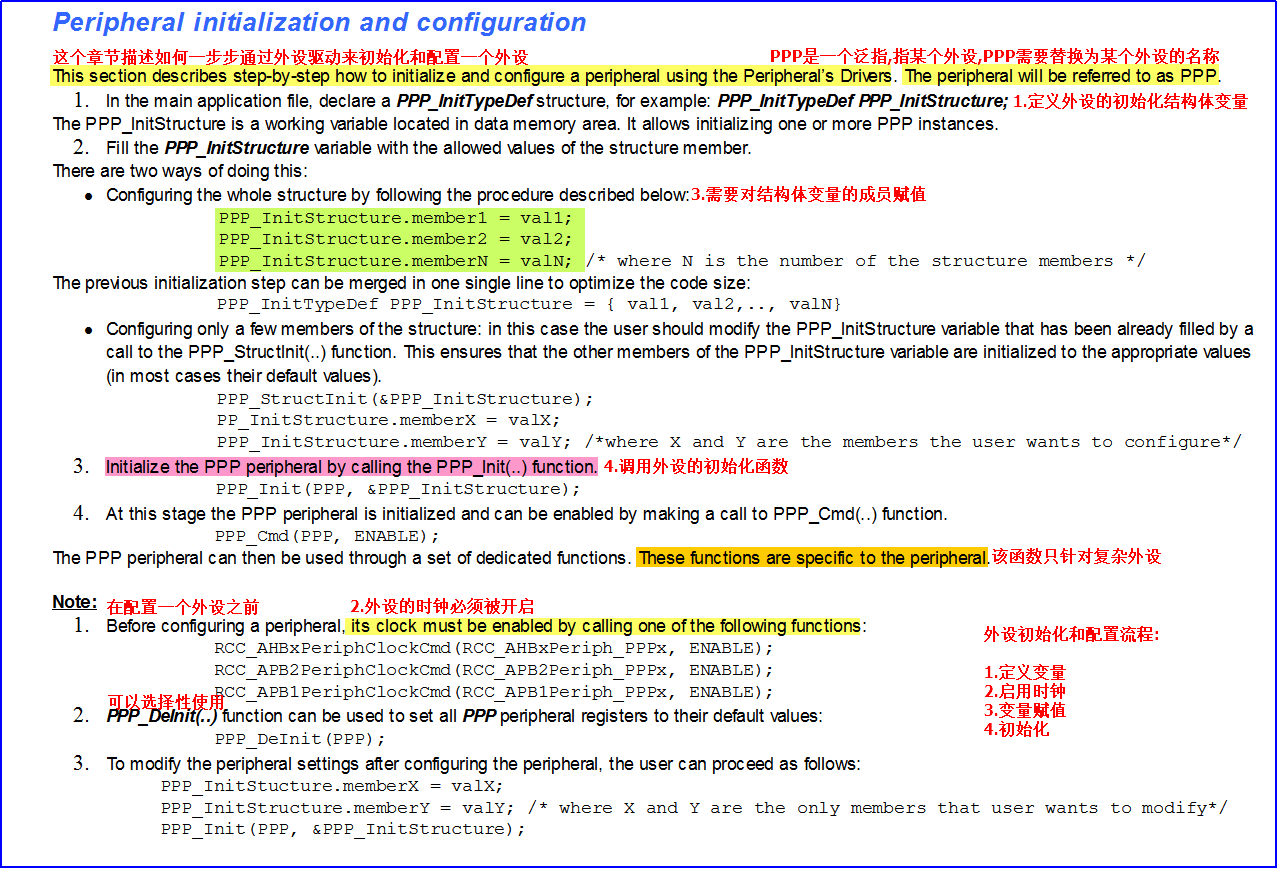

以上内容是ST公司官方提供的关于标准外设库(Standard Peripheral Library)的外设配置和初始化流程说明。这套流程涵盖了MCU(微控制器)中所有常见外设的配置方法,包括GPIO、USART、ADC、TIM等外设模块,具有很高的通用性和普适性。

ST公司考虑到不同开发者在实际项目中的需求可能存在差异,为了帮助开发者快速上手并正确使用这些外设,特别编写了大量详细的代码示例和参考案例。这些案例不仅包含了基本功能实现,还覆盖了各种典型应用场景下的配置方法,开发者可以直接参考这些现成的代码来加速自己的项目开发,大大提升了开发效率和用户体验。

练习:根据ST公司提供的关于GPIO外设的demo,实现控制开发板的PF9对应的LED灯点亮。

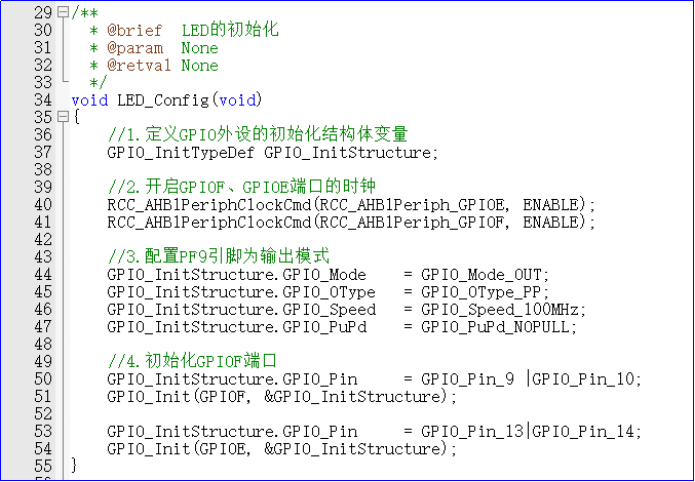

练习:根据ST公司提供的关于GPIO外设的demo,实现控制开发板的4盏LED灯全部点亮。